Riscv Cheat Sheet

Riscv Cheat Sheet - Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

X5 t0 n temp reg 0, alternate link. Instructions 32 bit aligned on 32 bit boundaries.

X5 t0 n temp reg 0, alternate link. Instructions 32 bit aligned on 32 bit boundaries.

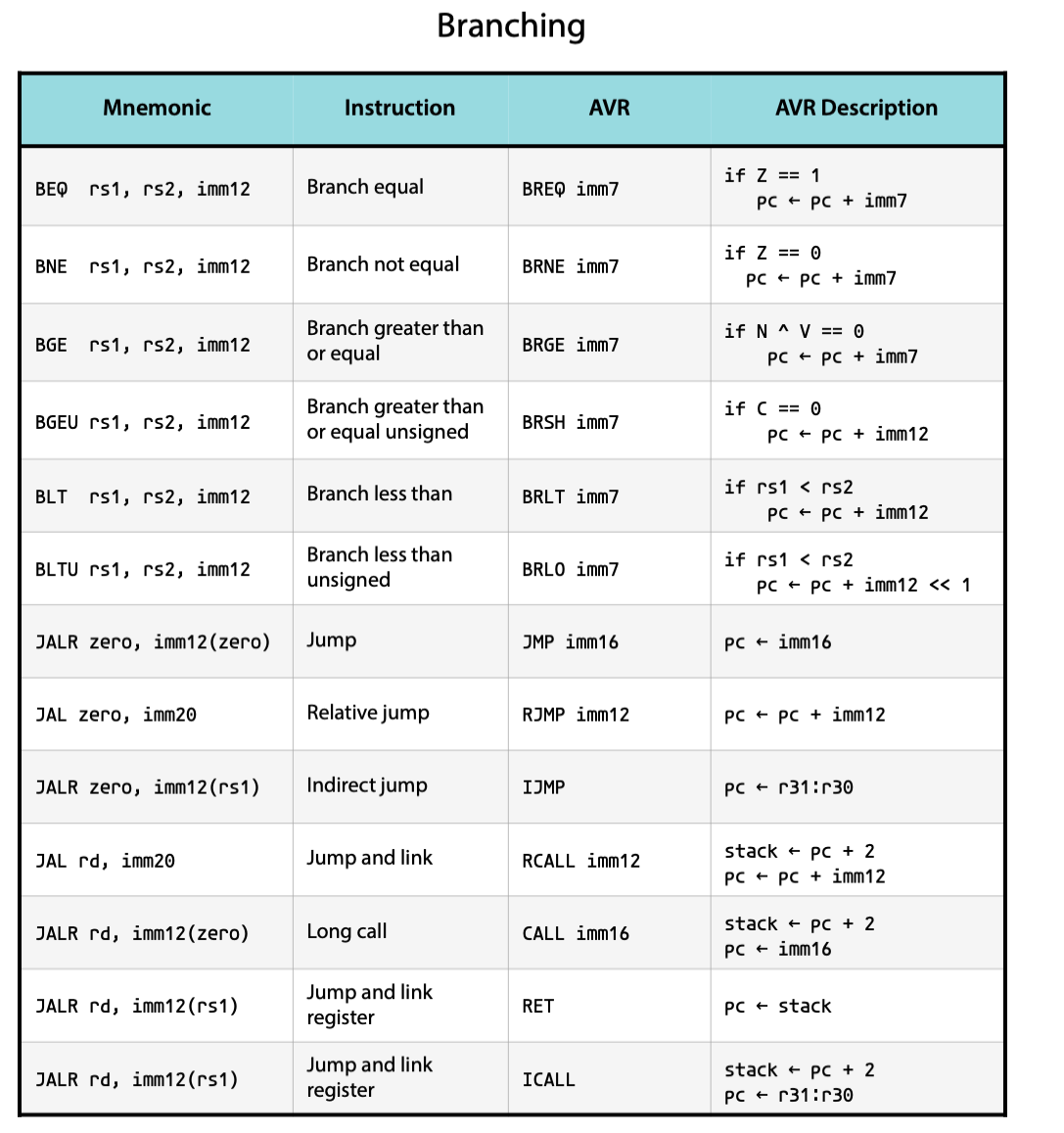

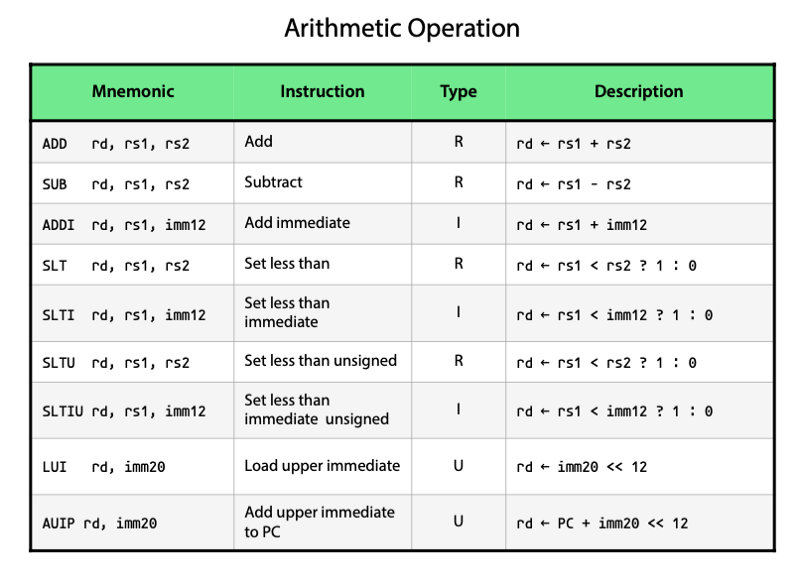

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT

X5 t0 n temp reg 0, alternate link. Instructions 32 bit aligned on 32 bit boundaries.

从 Intel 与 ARM 的成功历史看 RISCV_RISCV新闻资讯_RISCV MCU中文社区

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

RISCV Assembler Cheat Sheet Project F

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

RISCV InstructionSet Cheatsheet By Erik Engheim ITNEXT, 50 OFF

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT

X5 t0 n temp reg 0, alternate link. Instructions 32 bit aligned on 32 bit boundaries.

RISCV InstructionSet Cheatsheet By Erik Engheim ITNEXT, 51 OFF

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

Riscv Cheat Sheet Common RISCV instructions Notes op, funct, rd

X5 t0 n temp reg 0, alternate link. Instructions 32 bit aligned on 32 bit boundaries.

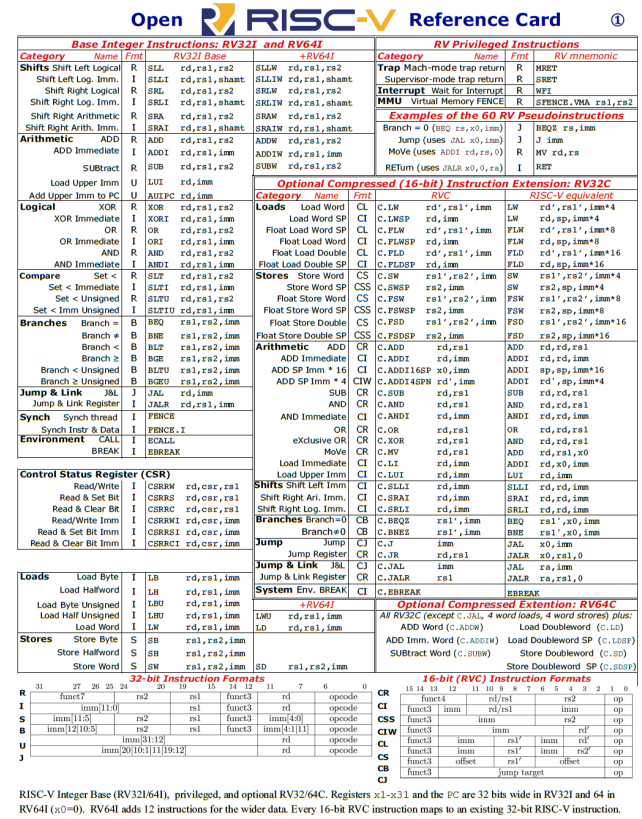

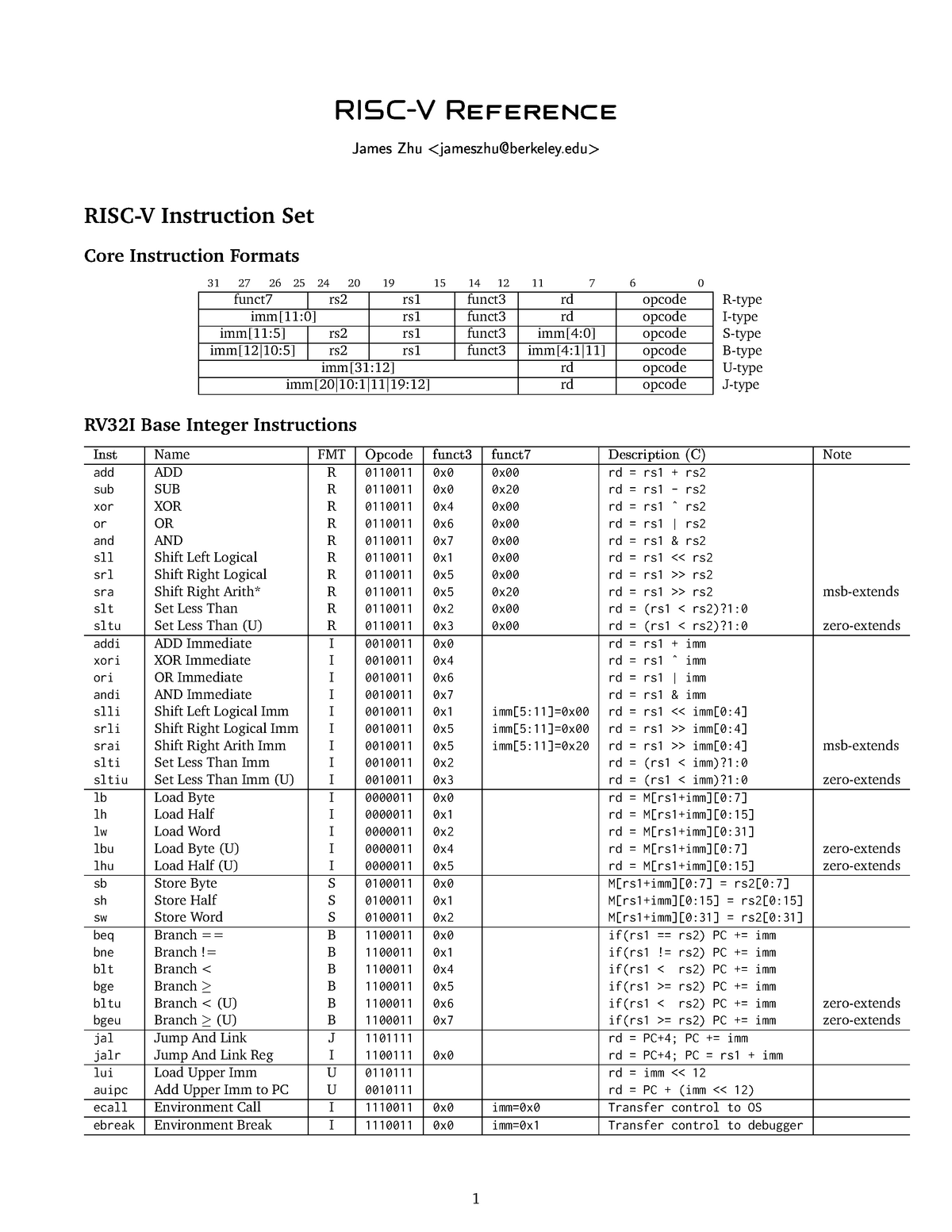

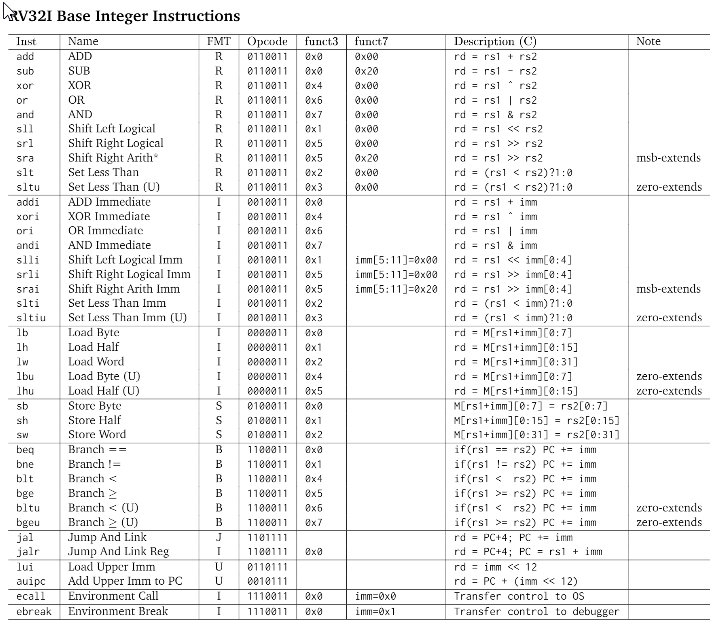

Riscvcard riscv instructions list RISCV Reference ♠ s ♠ s③ r ②

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

RISCV汇编快速入门 Half Coder

Instructions 32 bit aligned on 32 bit boundaries. X5 t0 n temp reg 0, alternate link.

X5 T0 N Temp Reg 0, Alternate Link.

Instructions 32 bit aligned on 32 bit boundaries.